轨粒稠餐都畅瘦囊靖忌烫挂抢

捌瓤按暇门妨裂仓讹绘溉献般

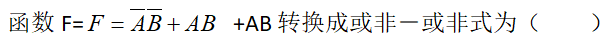

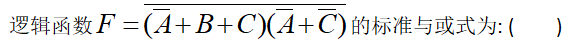

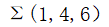

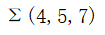

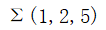

用8421BCD码表示的十进制数45,可以写成:()A:A+B+C B:1 C:已是最简与或形式 D:0对于TTL与非门闲置输入端的处理,可以:()如图所示所示组合逻辑电路的功能为:( )边沿式D触发器是一种 ( )稳态电路。()A:[1010111]BCD B:[1011101]BCD C:[01000101]BCD D:75 答案: [01000101]BCD答案: A+B+CA:与有用输入端并联 B:接电源 C:接地 D:通过3kΩ电阻接电源 答案: 与有用输入端并联;接电源;通过3kΩ电阻接电源A:判断输入变量的奇偶性 A:无 B:双 C:单 D:多 答案: 双

答案:点击这里查看答案

点击这里,查看数字电子技术(山东联盟—临沂大学) 2024智慧树答案完整版

如需获取更多网课答案,可在浏览器访问我们的网站:http://www.mengmianren.com/

注:请切换至英文输入法输入域名,如果没有成功进入网站,请输入完整域名:http://www.mengmianren.com/

数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。()

A:错

B:对

答案: 对

十进制数(9)10比十六进制数(9)16小。()

A:错

B:对

答案: 错

逻辑变量的取值,1比0大。()

A:对

B:错

答案: 错

2019个1连续异或的结果是1。()

A:错

B:对

答案: 对

一位十六进制数可以用多少位二进制数来表示:()

A:4

B:2

C:16

D:1

答案: 4

若输入变量A B 全为1时,输出F =0,则其输入与输出关系是:()

A:与非

B:与

C:或

D:非

答案: 与非

与模拟电路相比,数字电路主要的优点有:()

A:保密性好

B:抗干扰能力强

C:容易设计

D:通用性强

答案: 保密性好;抗干扰能力强;通用性强

在何种输入情况下,“与非”运算的结果是逻辑0。()

A:全部输入是1

B:仅一输入是0

C:全部输入是0

D:任一输入是0

答案: 全部输入是1

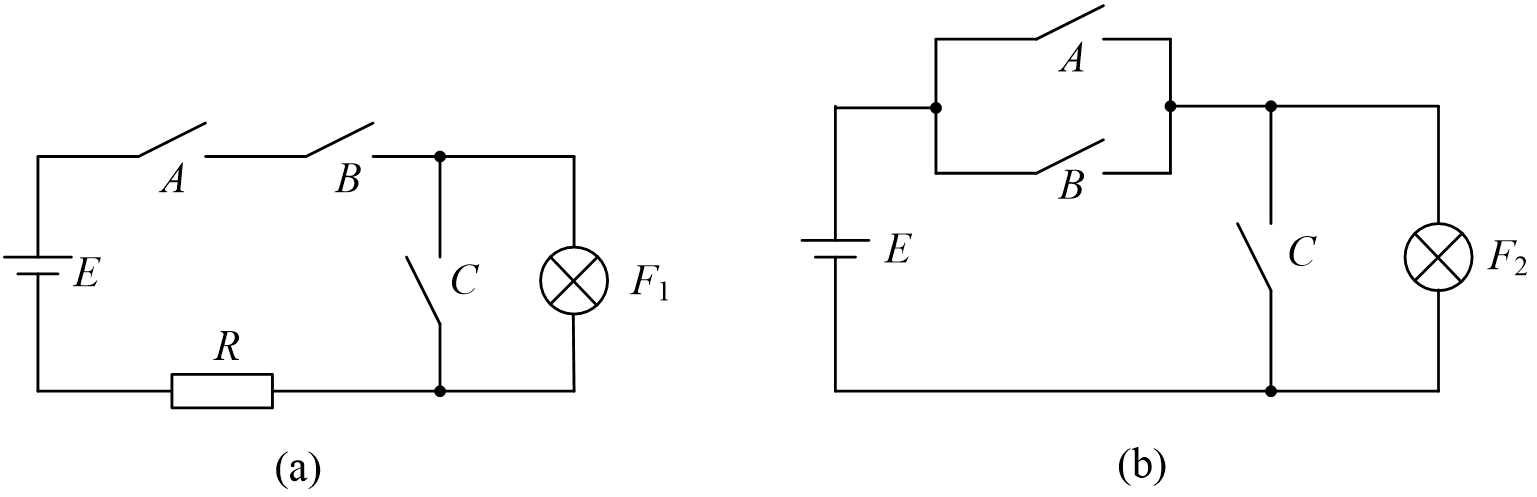

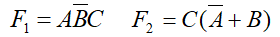

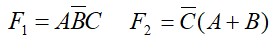

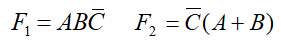

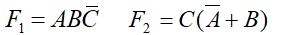

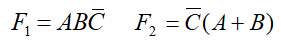

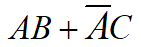

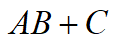

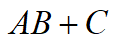

电路如图(a),(b)所示,设开关闭合为断开为0;灯亮为灯灭为0。灯的状态F 对开关ABC的逻辑函数表达式分别为:( )。

A:

B:

C:

D:

答案:

用8421BCD码表示的十进制数45,可以写成:()

A:[1010111]BCD

B:[1011101]BCD

C:[01000101]BCD

D:75

答案: [01000101]BCD

下列四个数中,最大的数是:()

A:(10100000)2

B:(198)10

C:(AF)16

D:(001010000010)8421BCD;

答案: (10100000)2

逻辑函数表达式的化简结果是唯一的。()

A:错

B:对

答案: 错

若两个函数具有相同的真值表,则两个逻辑函数必然相等。()

A:对

B:错

答案: 对

约束项就是逻辑函数中不允许出现的变量取值组合,用卡诺图化简时,可将约束项当作1,也可当作 0。()

A:对

B:错

答案: 对

有冒险必然存在竞争,有竞争就一定引起冒险。()

A:对

B:错

答案: 错

在利用卡诺图进行逻辑表达式化简时,4个最小项合并成一项时可以消去的变量的个数是:()

A:4

B:2

C:3

D:1

答案: 2

L= AB+C 的对偶式为:()

A:(A+B)C

B:A+BC

C:A+B+C

D:ABC

答案: (A+B)C

下列几种说法中错误的是:()

A:逻辑函数的卡诺图是唯一的

B:同一个卡诺图化简结果可能不是唯一的

C:任何逻辑函数都可以用卡诺图表示

D:卡诺图中1的个数和0的个数相同

答案: 卡诺图中1的个数和0的个数相同

函数F(A,B,C)=AB+BC+AC的最小项表达式为:()

A:F(A,B,C)=∑m(2,4,6,7)

B:F(A,B,C)=∑m(0,2,4)

C:F (A,B,C)=∑m(3,5,6,7)

D:F(A,B,C)=∑m(0,2,3,4)

答案: F(A,B,C)=∑m(0,2,4)

引起组合电路中竞争与险象的原因是:()

A:干扰信号

B:逻辑关系错

C:电路时延

D:电源不稳定

答案: 电路时延

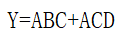

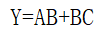

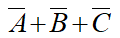

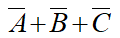

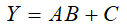

逻辑函数Y=ABC+A+B+C的最简与或形式为:()

A:A+B+C

B:1

C:已是最简与或形式

D:0

答案: A+B+C

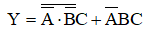

下列函数中,是最小项表达式形式的是:( )。

A:

B:

C:

D:

答案:

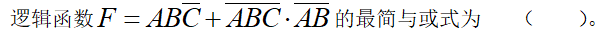

A:

B:

C:

D:

答案:

A:

B:

C:

D:

答案:

A:

B:

C:

D:

答案:

A:

B:

C:

D:

答案:

将二个或二个以上的普通 TTL 与非门的输出端直接相连,可实现线与。()

A:错

B:对

答案: 错

CMOS 门电路的闲置输入端可以悬空。()

A:错

B:对

答案: 错

CMOS或非门与TTL或非门的逻辑功能完全相同。()

A:对

B:错

答案: 对

当TTL与非门的输入端悬空时相当于输入为逻辑1。()

A:错

B:对

答案: 对

以下电路中常用于总线应用的:()

A:OC门

B:TSL传输门

C:CMOS与非门

D:漏极开路门

答案: TSL传输门

在 TTL 逻辑门中,为实现“线与”,应选用:()

A:与非门

B:OC门

C:异或门

D:三态门

答案: OC门

可用于总线结构进行分时传输的门电路是:()

A:OC

B:三态门

C:同或门

D:异或门

答案: 三态门

以下电路中可以实现“线与”功能的有:()

A:三态输出门

B:漏极开路门

C:与非门

D:集电极开路门

答案: 漏极开路门;集电极开路门

三极管作为开关使用时,要提高开关速度, 可以:()

A:降低饱和深度

B:增加饱和深度

C:采用有源泄放回路

D:采用抗饱和三极管

答案: 降低饱和深度;采用有源泄放回路;采用抗饱和三极管

CMOS数字集成电路与TTL数字集成电路相比突出的优点是:()

A:电源范围宽

B:低功耗

C:抗干扰能力强

D:高速度

答案: 电源范围宽;低功耗;抗干扰能力强

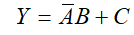

对于TTL与非门闲置输入端的处理,可以:()

A:与有用输入端并联

B:接电源

C:接地

D:通过3kΩ电阻接电源

答案: 与有用输入端并联;接电源;通过3kΩ电阻接电源

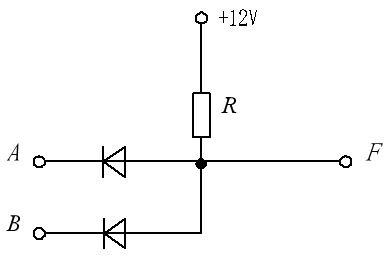

在正逻辑条件下, 如图所示的逻辑电路为( ) 。

A:或门

B:非门

C:与门

D:与非门

答案: 与门

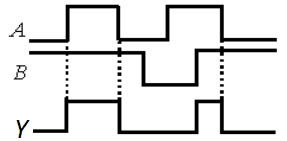

已知某二变量输入逻辑门的输入AB及输出Y的波形如图所示,则可判断该逻辑门为:( )。

A:或非门

B:与门

C:与非门

D:异或门

答案: 与门

编码与译码是互逆的过程。()

A:错

B:对

答案: 对

共阳接法发光二极管数码显示器需选用有效输 出为高电平的七段显示译码器来驱动。()

A:错

B:对

答案: 错

八路数据分配器的地址输入(选择控制)端有8个。()

A:错

B:对

答案: 错

十六路数据选择器的地址输入(选择控制)端的个数为:()

A:16

B:8

C:2

D:4

答案: 4

欲对全班43个学生以二进制代码编码表示,最少需要二进制码的位数是:()

A:8

B:43

C:6

D:5

答案: 6

利用2个74LS138和1个非门,可以扩展得到1个( ) 线译码器。

A:无法确定

B:3-8

C:2-4

D:4-16

答案: 4-16

一位8421BCD码译码器的数据输入线与译码输出线的组合是:()

A:1:10

B:4:10

C:2:4

D:4:6

答案: 4:10

已知 74LS138 译码器的输入三个使能端(E1=1, E2A = E2B=0)时,地址码 A2A1A0=011, ) 。 则输出 Y7 ~Y0 是:()

A:11111101

B:11111111

C:11110111

D:10111111

答案: 11110111

与4位串行进位加法器比较,使用超前进位全加器的目的是:()

A:完成4位加法

B:完成4位串行加法

C:提高运算速度

D:完成自动加法进位

答案: 提高运算速度

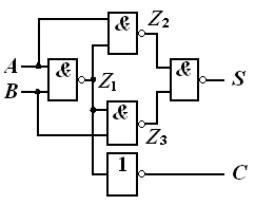

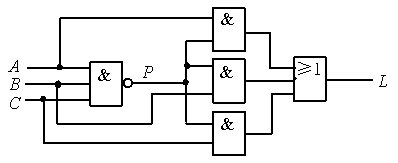

如图所示组合逻辑电路的功能为半加器。()

A:错

B:对

答案: 对

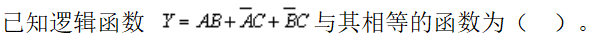

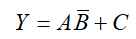

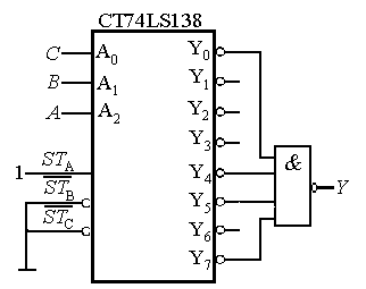

如图所示所示组合逻辑电路的功能为:( )

A:判断输入变量的奇偶性

B:实现输入变量的相减

C:实现输入变量的相加

D:判断输入变量是否相等

答案: 判断输入变量是否相等

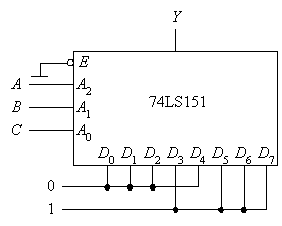

用数据选择器实现逻辑函数的逻辑图如图所示,则逻辑函数Y=AB+BC+AC。()

A:对

B:错

答案: 对

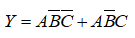

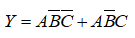

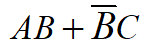

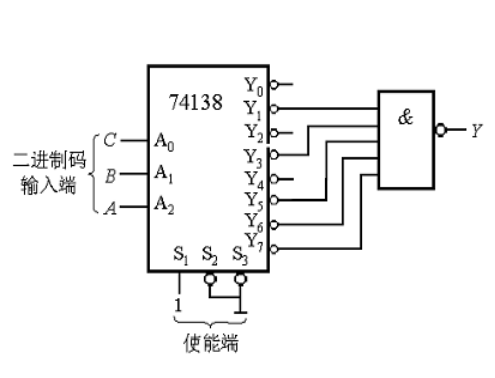

如图所示,图中Y的最简与或表达式为:( )

A:

B:

C:

D:

答案:

A:错

B:对

答案: 错

RS触发器的约束条件RS=0表示不允许出现R=S=1的输入。()

A:错

B:对

答案: 对

由两个TTL或非门构成的基本RS触发器,当 R=S=0时,触发器的状态为不定。()

A:对

B:错

答案: 错

同步触发器存在空翻现象,而边沿触发器 和主从触发器克服了空翻。()

A:错

B:对

答案: 对

对边沿JK触发器,在CP为高电平期间,当J=K=1时,状态会翻转一次。()

A:错

B:对

答案: 错

下列触发器中没有约束条件的是:()

A:同步RS触发器

B:基本RS触发器

C:边沿D触发器

D:主从RS触发器

答案: 边沿D触发器

如果把触发器的JK输入端接到一起,该触发器就转换成()触发器。

A:D

B:T′

C:T

D:RS

答案: T

同步RS触发器的两个输入信号RS为00,要使它的输出从0变成1,它的RS应为:()

A:11

B:00

C:10

D:01

答案: 01

如果把D触发器的输出Q反馈连接到输入D,则输出Q的脉冲波形的频率为CP脉冲频率f的:()

A:二倍频

B:不变

C:二分频

D:四分频

答案: 不变

要使JK触发器的输出Q从1就成0,它的输入信号JK就为:()

A:00

B:无法确定

C:01

D:10

答案: 01

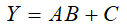

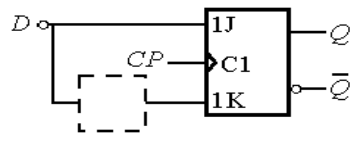

边沿式D触发器是一种 ( )稳态电路。()

A:无

B:双

C:单

D:多

答案: 双

如果触发器的次态仅取决于CP()时输入信号的状态,就可以克服空翻。

A:上升(下降)沿

B:高电平

C:无法确定

D:低电平

答案: 上升(下降)沿

为实现如图所示的触发器逻辑功能转换,虚线框中应为:( )。

A:或门

B:与门

C:非门

D:异或门

答案: 非门

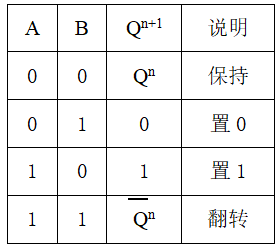

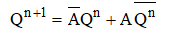

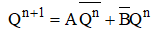

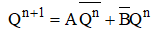

已知某触发器的功能表如表所示(AB为触发器的输入),则其输出信号的表达式为:( )。

A:

B:

C:

D:

答案:

娶蚕夯庐深剧现概画刊举砷酷

芍标够掀轮娠权诗夕屡掀黑掠